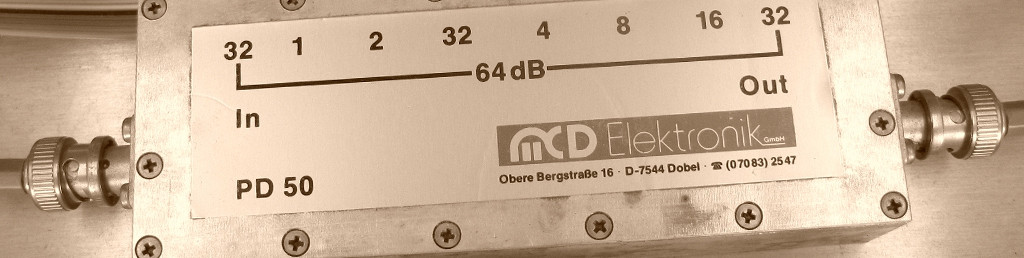

Der LVDS-Analyzer wurde als Teil eines Testsystems entwickelt. Mit dem Analyzer kann die digitale Farbinformation einer beliebigen Videozeile innerhalb eines Bildes erfasst und ausgewertet werden. Dazu wird das 2-Draht LVDS-Signal deserialisiert und die darin enthaltenen Informationen erfasst. Das Testbild kann 1 zu 1 auf ein Referenz-Display weitergeleitet oder eigene Testbilder auf zu prüfende LVDS-Senken ausgegeben werden.

Allgemein:

- Spannungsversorgung 5V über den USB-Anschluss

- Steuerung und Datenübertragung über USB 2.0 (auf Anfrage auch über RS232)

- Nutzung der Diagnose- und Steuerfunktionen der LVDS-Serialiser und -Deserialiser wie:

- Erkennung LVDS-Kabelfehler (Kurzschluss, Unterbrechung) am LVDS-Ausgang

- Erkennung einer vorhandenen Verbindung (Lock-Signal) am LVDS-Eingang

- Fernkonfiguration der LVDS-Gegenstelle an Ein- und Ausgang (muss von dieser unterstützt werden)

- Deserialiser und Serialiser über USB ein- und ausschaltbar während anderer besonders störsensibler Prüfvorgänge

LVDS-Eingang

- Deserialisierung der LVDS-Datenströme mit MAX9260 von Maxim Integrated Products Inc.

- Demapping des empfangenen Video-Datenstroms in RGB-Daten, HSYNC und VSYNC

- Analoge Ausgabe des I²S-Audiodatenstroms über Digital/Analog-Wandler

- Serialisierte LVDS-Ausgabe des Video- und Audio-Eingangsdatenstroms über MAX9259 von Integrated Products Inc.

- Remapping des Ausgangsdatenstroms für unterschiedliche Zielgeräte (Displays) möglich.

- Messen der Bildgeometrie mittels Erfassung von HSYNC, VSYNC und Pixeltakt

- Erfassung einer Videozeile in voller Auflösung mit bis zu 2047 Pixeln

- RGB-Farbauflösung bis zu 24Bit

- Erfassung eines Standbildes per mehrfacher Zeilenabtastung möglich

- Reduzierung der Auflösung zur Erhöhung der Messgeschwindigkeit möglich

LVDS-Ausgang

- Frei definierbares Balkentestbild mit bis zu 2047 Pixel Breite und bis zu 2047 Zeilen Höhe; auch horizontale Grau- und Farbverläufe möglich

- RGB-Farbauflösung bis zu 24Bit

- Mapping der Farb- und Synchronsignale auf das Zielgerät (LVDS-Senke)

- Synchronisierbar auf die Synchronsignale des Eingangs

- Generierung eigener Synchronsignale HSYNC, VSYNC und DATA ENABLE aus dem Pixeltakt

- Wahlweise Pixeltakt aus Eingangssignal oder eigener Taktgenerator (18MHz, 27MHz, 29MHz, 36MHz, 54MHz, 58MHz)